1U Clock Divider

Mit diesem Clock Divider für Eurorack Modularsynthesizer erhältst Du die nötige Portion Polyrhythmik, die deine Tracks richtig zum Leben erweckt.

Eingesetzt als Sub-Oscillator verpasst du deinem VCO ordentlich Druck untenrum und über die ungeraden Teiler sind auch subharmonische Moll-Akkorde wie im Trautonium möglich.

Dies ist ein kompakter Clock Divider zum Einbau in 1U-Reihen von Eurorack-kompatiblen Modularsynthesizer-Systemen. Das eingespeiste Clock-Signal wird an sieben Ausgängen mit unterschiedlichen Teilverhältnissen zur Verfügung gestellt. Die Ausgänge sind als Puls-Ausgänge konfiguriert und stellen einen Puls in der Länge eines positiven Clock-Ticks zur Verfügung. Sieben LEDs zeigen die Zustände der Ausgänge an. Ein Reset-Eingang ermöglicht das rücksetzten des Clock-Dividers vor einem kompletten Zählvorgang.

Zusätzlich ist ein logischer UND-Baustein mit zwei Eingängen integriert.

Mit den geraden und ungeraden Teilerverhältnissen von Clock/2 bis Clock/8 lassen sich zum Beispiel Polyrhythmiken oder ungewöhnliche Sequenzen erzeugen.

Wird der Ausgang eines VCO in den Clock-Input gesteckt, lässt sich das Modul als Suboszillator oder Subharmonikgenerator verwenden. Die Divider Ausgänge können dann über einen Mixer oder Filter zusammengemischt werden um subharmonische Moll-Akkorde wie im Trautonium oder Subbässe zu erzeugen.

Eigenschaften:

- Takteingang (Uhrsymbol)

- Reset-Eingang (Reset-Symbol) Der Reset-Eingang des Clock-Teilers ist auf den AND-Ausgang normalisiert.

- Teilerausgänge (/2 bis /8)

- UND-Gatter (zwei Eingänge, ein Ausgang)

- Acht LEDs zeigen den Zustand der Ausgänge an

- basierend auf CGS36 von Ken Stone

- 1HE-Tile (Intellijel-Format)

- Beidseitig bedrucktes FR4-Panel

Patch Beispiele

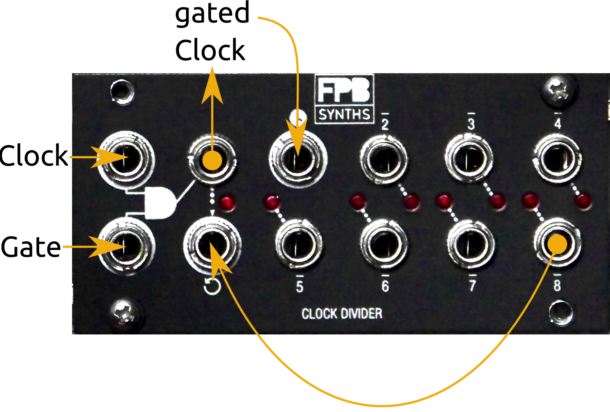

Beispiel A

- Eingänge: Clock und Gate

- Ausgang: Gated Clock, kann auf Clock-Eingang gepatcht werden

Während Gate high ist, läuft der Clock-Teiler mit Clock-Geschwindigkeit. Bei Audiofrequenz ist der Ton zu hören (einfacher VCA/Gate). Da der Reset-Eingang auf den UND-Ausgang normiert ist, muss dieser auf einen geraden Teiler (z.B. /8) gelegt werden.

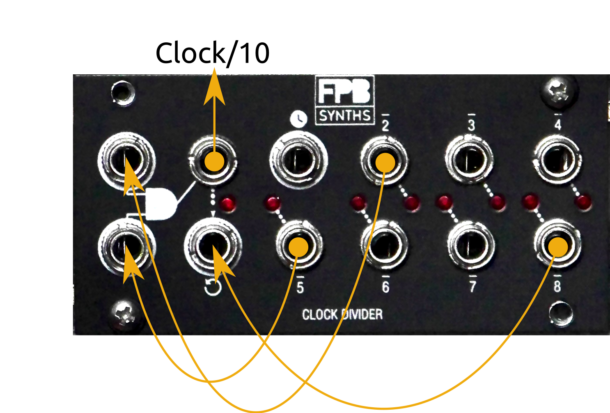

Beispiel B

- Eingänge: zwei verschiedene Teiler

- Ausgang: neuer Teiler mit Teilung Clock/n [n = UND-Eingang 1 * UND-Eingang 2]

Da der Reset-Eingang auf den UND-Ausgang normiert ist, muss dieser auf einen geraden Teiler (z.B. /8) gelegt werden. Für mehr Chaos können aber auch andere Teilerverhältnisse oder ein LFO an den Reset angeschlossen werden.